Phase locked loop (PLL)

Phase locked loop (PLL)

PLL is a feedback control circuit that uses the external input reference signal to control the oscillating signal within the loop and output accurate frequency and phase.

Key Features

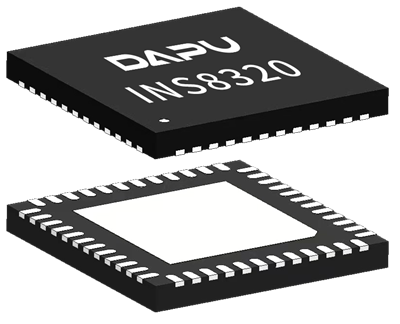

The INS83XX series of PLL chips feature extremely low phase noise and jitter, programmable bandwidth, dual PLL, support for input and output of any frequency, and clock accuracy better than 0.05ppm in hold mode.

Applications

PLL with low jitter

| Type | Output channel | Output level | Output freq. (MHz) | RMS jitter (fs) | Input channel | Input level | Voltage |

|---|---|---|---|---|---|---|---|

| INS8320 | 14 | LVDS/ LVPECL/ LVCMOS | DC ~ 3000 | < 125 | 3 | LVDS/ LVPECL/ LVCMOS/ Crystal | 3.3 |

RF PLL with Low noise

| Type | Integrated VCO | Normalized phase noise (dBc/Hz) | Max. output freq. (GHz) |

|---|---|---|---|

| INS85XX | Y | -230 | 10 |